The Samraksh Company

## Users Manual for the GuardBee

An Ultra Low-Power, FPGA-Based Motion Detection Module

Manual Version 1.0.0 Edited April 14, 2011 (The latest version of this manual can be downloaded from www.samraksh.com)

## 1. Introduction

The GuardBee is an ultra low-power motion detection module that is designed for commercial applications in Wireless Sensor Networks (WSNs). The GuardBee integrates Samraksh's popular BumbleBee Pulsed Doppler Radar (PDR) with an ultra low power FPGA platform that eliminates the need for additional mote hardware for signal processing.

The GuardBee hardware platform includes a Doppler radar based sensing module, an FPGA for computing and all of the required circuitry for signal conditioning, sampling and user interface. The GuardBee also ships pre-packaged to facilitate easy deployment in a variety of indoor and outdoor settings.

The GuardBee software platform features a Verilog implementation of drivers for ADC sampling, IO control logic and a fully functional port of Samraksh's proprietary *Displacement Detection* algorithm for robust motion detection.

Key features of the GuardBee include:

- A detection range up to 10m.

- Single-device solution with on-board FPGA processing.

- 40mW power consumption, including 0.1mW for the FPGA.

- Two-wire interrupt style GPIO output for integration with external devices.

- Optional SPI bus connection for integration with external networking or microcontroller modules.

## 2. Contents of the Box

An enclosed GuardBee module ships fully assembled (minus batteries) and consists of the following key components:

- A customized plastic enclosure with mounting support for electronics and cutouts for user interfaces

- GuardBee board (mounted)

- Doppler Radar Sensor board (mounted)

- Battery pack (mounted)

- Connectors for inter-board connections

- LED for visual user notification

- 3-wire connector for digital integration

If the contents of your box differ from this and you purchased your devices from our web site, please contact technical support at <u>support@samarksh.com</u>. Note that devices not-purchased on the web, typically larger orders, may contain other contents as negotiated at the time of purchase. If this is your case but your box doesn't contain what you expected, please contact <u>sales@samraksh.com</u>.

## 3. GuardBee board and Connection headers

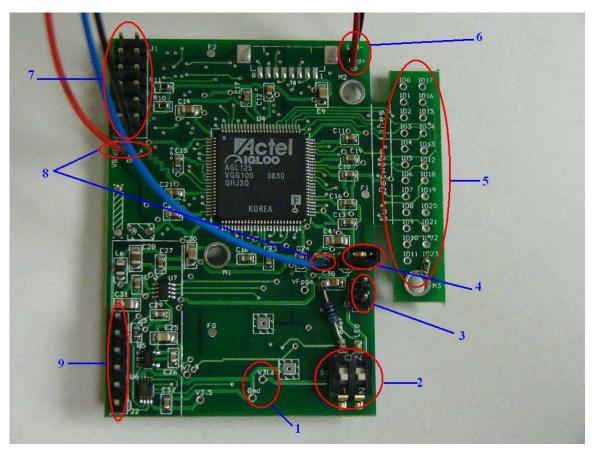

The GuardBee board has the following layout. Highlighted sections of the board are explained below:

- 1. **Power**: Connect the battery inputs to the device across V3Li and Gnd. For assembled units, these inputs are connected to a 3xD battery holder. For long lived operation (up to 6 months), we recommend using 3 D-sized high capacity Lithium Thionyl Chloride batteries, nominally rated at 19Ah @ 3.6V. An example of such a battery is <a href="http://www.xenousa.com/pdf/XL-205F.pdf">http://www.xenousa.com/pdf/XL-205F.pdf</a>. The GuardBee can accept input voltages at the V3Li terminal of up to 15V.

- 2. Switches: Switch 1 controls power to the main GuardBee board and the rest of the circuits. Switch 2 controls whether or not the LED should be used by the device. The LED control logic is deigned to signal target detection using the LED only if Switch 2 is ON. Users may wish to leave switch 2 ON forever to get visual confirmation that the device is functional. However, in some cases such as outdoor deployment where the LED cannot be seen clearly or indoor deployments where stealth is desired, the LED switch may be turned ON initially to verify device functioning and then turned OFF.

- 3. **Programming Power (J3)**: Under normal operating conditions, the FPGA runs at 1.2V to minimize power consumption but for programming purposes, a higher voltage of 1.5V

is required. The J3 header is used to supply power to the device while programming the FPGA. The ground pin on the header has a marking on the white silkscreen.

- 4. **Signaling voltage control (J5)**: The GuardBee device signals target detection digitally using a GPIO line (see 8). The operating voltage for this IO line may be provided by the GuardBee itself, or by the device receiving this signal. If the internal signaling voltage of 3.3V is acceptable for the external device, the two pins of J5 can be shorted using the jumper. However, if users wish to provide their own interfacing voltage, the jumper across J5 should be removed.

- 5. **Debug IO lines**: 24 General purpose IO lines from the FPGA are exposed in a breakout section. These are useful for debugging purposes for users who wish to program the FPGA on their own. The GPIO debug lines operate either at the internal voltage level of 3.3V if J5 is shorted or at the user-specified IO signaling level if J5 is open. The pin IO23 is reserved.

- 6. **LED**: The Led through holes are used to connect a panel mount LED to the GuardBee so that it can be seen from the outside of the enclosure. For assembled units. The LED is already panel mounted.

- 7. **JTAG programming header**: The JTAG programming header is used to reflash the Actel FPGA and is fully pin compatible with the 12-pin connector on Actel Low Cost Programmer Stick (LCPS) which uses the FlashPro technology.

- 8. **External connector**: The external connector is used to signal target detection to an external device. Pin 1 (black wire) on the connector is ground. Pin 2 (blue wire) is the detection line and it is active low. Pin 3 (red wire) may be used to provide an external voltage to the GuardBee for signaling purposes. This voltage may be in the 1.2V-3.6V range. This external voltage will also be used to power the debug IO lines and the user must ensure that it is capable of providing enough current to power the IO lines.

- 9. **Radar connector**: The 6-pin radar connector is used to connect the BumbleBee radar to the GuardBee board. The GuardBee provides power to the BumbleBee using onboard voltage regulators so no separate battery pack is required for the BumbleBee. Conversely, the output signals produced by the BumbleBee are brought on to the GuardBee board where they may be sampled and consumed by the algorithm running on the FPGA. The pinout for the radar connector is as follows:

- a. Pin 1 : Ground (mates with J1-1 on the BumbleBee)

- b. Pin 2: Radar ON (mates with J1-3 on the BumbleBee)

- c. Pin 3: Radar power (mates with J1-2 on the BumbleBee)

- d. Pin 4: Ground (mates with J2-1 on the BumbleBee)

- e. Pin 5: Radar I channel (mates with J2-2 on the BumbleBee)

- f. Pin 6: Radar Q channel (mates with J2-4 on the BumbleBee)